# The University of Texas at Arlington

# Lecture 11 Interrupts

## CSE 3442/5442 Embedded Systems 1

Based heavily on slides by Dr. Gergely Záruba and Dr. Roger Walker

# **External PIC Influence**

- We don't always just want data transfer from pin connections (input or output)

- Regardless of the data's value, the same actions are performed

- Instead we can have the values on pin connections influence or control which segments of code/functions are used

- Based off input, we can handle things in a different particular manner

- An <u>Interrupt</u> uses hardware to cause special software execution

# **Polling vs. Interrupts**

## • Polling

- Continuously monitor the status of a device, bit, or pin

- When the condition is met, perform the service

- Wastes the PIC's time and resources

- Only "looking" at a single location

- Can get stuck (infinite loop) if condition is never met

- Could miss other important input data or events

```

while(1)

{

if(PORTBbits.RB0 == 1)

break;

}

//or

while(PORTBbits.RB0 == 0);

```

# **Polling vs. Interrupts**

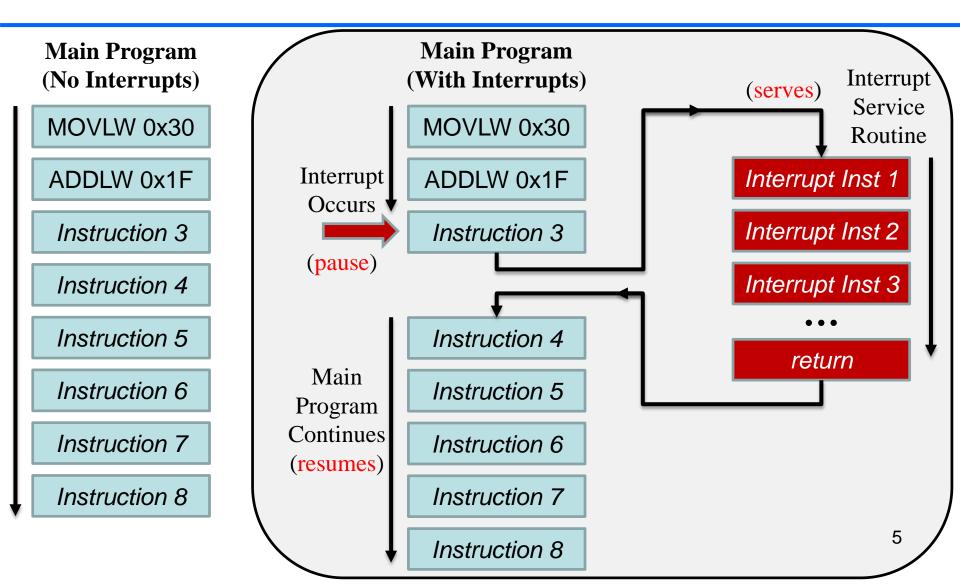

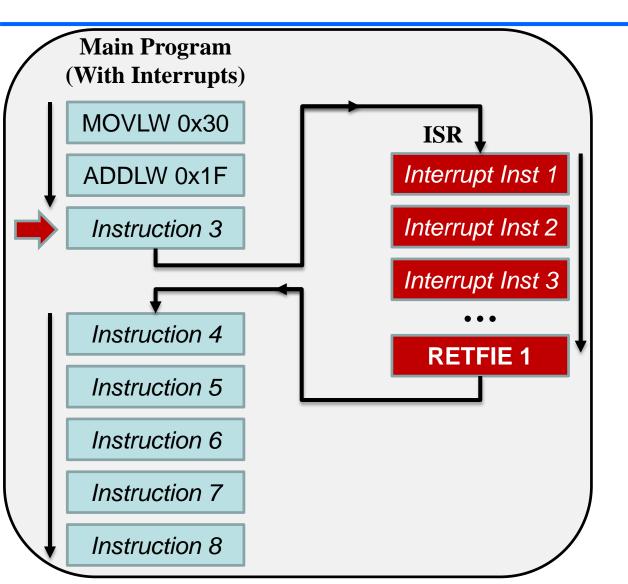

#### Interrupts

- Whenever a device (pin, peripheral) needs the PIC's service, it notifies by sending an interrupt signal

- Asynchronous (can happen at any time)

- When that signal is detected...

- PIC stops (pauses) its current actions

- Handles (serves) the source of the interrupt

- Returns exactly where the PIC left off (resumes)

- Doesn't bog-down the PIC's resources

- Can serve many devices (multiple interrupt sources)

- Each can get the PIC's attention at any time

- Can assign priorities to each interrupt

- "Interrupt an interrupt"

- Can also ignore (mask) interrupt sources at any time

- When sleeping, they can wake up the microcontroller

# **Interrupt Handling**

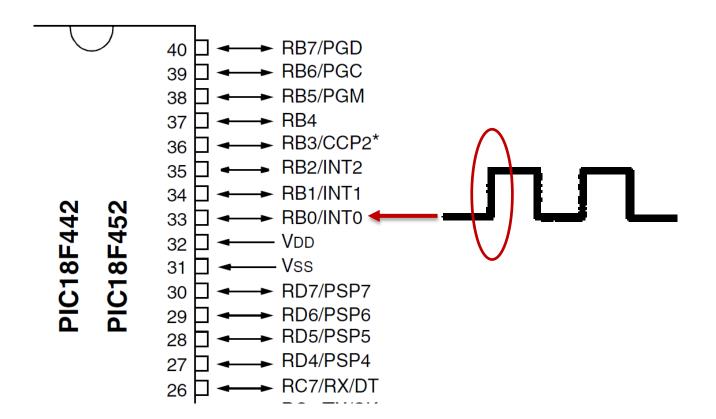

## **Basic Example**

When PORTB pin B0 is brought HIGH (1)

– Go to function → *Input\_Detected()*

# Basic Example (No Interrupts)

| <pre>void main() {     int a, b, c = 0;     while(1)     { //main program</pre>  |    | <pre>void main() {     int a, b, c = 0;     while(1)     { //main program</pre>                                       |

|----------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------|

| <pre> if(PORTBbits.B0 == 1) Input_Detected(); //main program continues }</pre>   | OR | <pre> while(PORTBbits.B0 == 0);     //wait here until B0 is 1 Input_Detected();     //main program continues  }</pre> |

| <pre>void Input_Detected() {     printf("Pin B0 is 1!!!\n");     return; }</pre> |    | <pre>void Input_Detected() {     printf("Pin B0 is 1!!!\n");     return; } </pre>                                     |

# Basic Example (With an Interrupt)

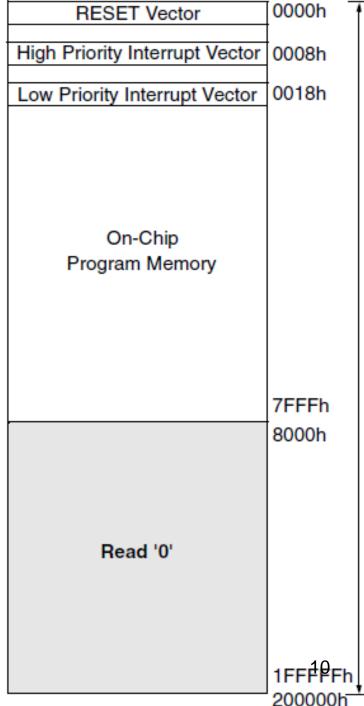

# **Interrupt Service Routines**

- Where to "jump" when an interrupt is triggered?

- Need a sub-routine to handle interrupts

- Interrupt Service Routines (ISR) serve that purpose

- The ISRs have a fixed location in Program ROM

If multiple ISRs, the group of locations is the interrupt vector table

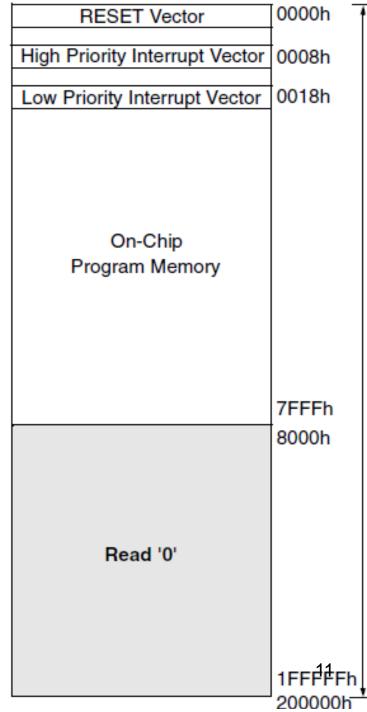

- PIC18 only has <u>three</u> locations to handle interrupts but we only have control of <u>two</u> of them for "normal" interrupts

- Program ROM: 0x0008 HIGH Priority

- Program ROM: 0x0018 LOW Priority

| Interrupt               | ROM Location (Hex)                 |

|-------------------------|------------------------------------|

| Power-on Reset          | 0000                               |

| High Priority Interrupt | 0008 (Default upon power-on reset) |

| Low Priority Interrupt  | 0018 (See Section 11.6)            |

9

#### Table 11-1: Interrupt Vector Table for the PIC18

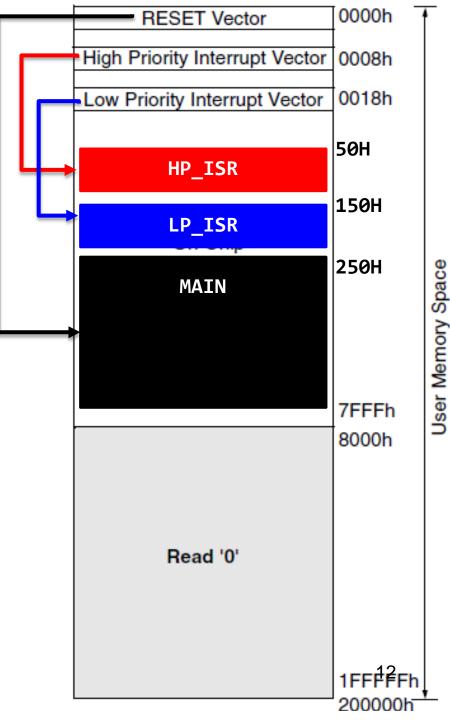

As there is limited space at these addresses it is a good idea to place a **GOTO** instruction at the interrupt vector jumping to a remote location

User Memory Space

| As there is limited space at these |             |              |  |  |  |  |

|------------------------------------|-------------|--------------|--|--|--|--|

| addresses it is a                  | a good id   | dea to place |  |  |  |  |

| a GOTO instruc                     | ction at tl | ne interrupt |  |  |  |  |

| vector jumping                     | to a rem    | ote location |  |  |  |  |

|                                    | ORG         | 0000H        |  |  |  |  |

|                                    | GOTO MAIN   |              |  |  |  |  |

|                                    | ORG         | 0008H        |  |  |  |  |

|                                    | GOTO        | HP_ISR       |  |  |  |  |

|                                    | ORG         | 0018H        |  |  |  |  |

|                                    | GOTO        | LP_ISR       |  |  |  |  |

|                                    |             |              |  |  |  |  |

|                                    | ORG         | 50H          |  |  |  |  |

| HP_ISR                             | •••         |              |  |  |  |  |

|                                    | ORG         | 150H         |  |  |  |  |

| LP_ISR                             | •••         |              |  |  |  |  |

|                                    | ORG         | 250H         |  |  |  |  |

MAIN

•••

As there is limited space at these addresses it is a good idea to place a **GOTO** instruction at the interrupt vector jumping to a remote location

|        | ORG<br>GOTO | 0000H<br>MAIN   |

|--------|-------------|-----------------|

|        | ORG<br>GOTO | 0008H<br>HP_ISR |

|        | ORG<br>GOTO | 0018H<br>LP_ISR |

| HP_ISR | ORG<br>     | 50H             |

| LP_ISR | ORG<br>     | 150H            |

| MAIN   | ORG<br>     | 250H            |

- The current instruction's execution is finished and the next instruction's address is pushed to the stack

Interrupts are disabled for HP (GIE or GIEH or GIEL cleared)

- 2. The PC is loaded with the interrupt vector – Jump to the ISR

- 3. The instructions in the ISR are executed until a **RETFIE** instruction

- Return From Interrupt Exit

- 4. RETFIE will cause the microcontroller to pop the PC from the stack and resume normal operations

- Interrupts are re-enabled (GIE or GIEH or GIEL set)

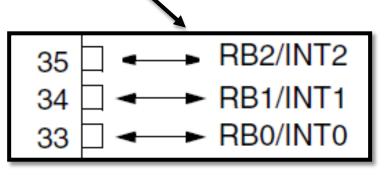

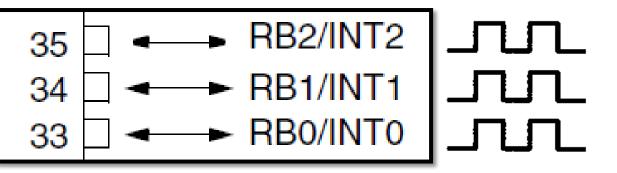

# **Sources of Interrupts**

- 1. Timers

- 2. Hardware Interrupts (external pins, INT)

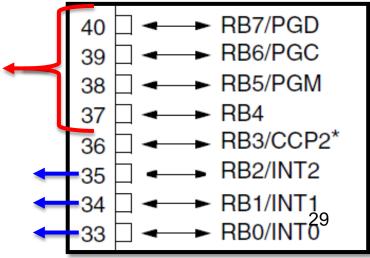

- PORTB: RB0, RB1, and RB2

- 3. Serial Communication

- Receive and Transmit

- 4. PORTB-Change

- 5. ADC

- 6. CCP/PWM

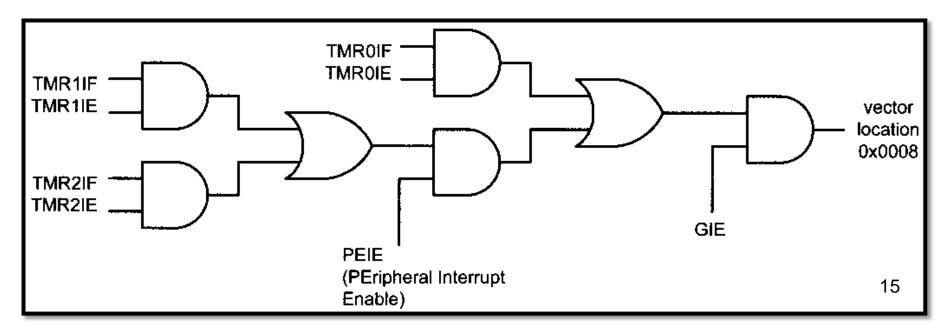

- We can easily think of an interrupt as **two** digital signals:

- Enable bit can allow/disallow the actual interrupt from happening (Enabled = Unmasked, Disabled = Masked)

- 2. Flag bit is set if interrupt should be invoked (something happened)

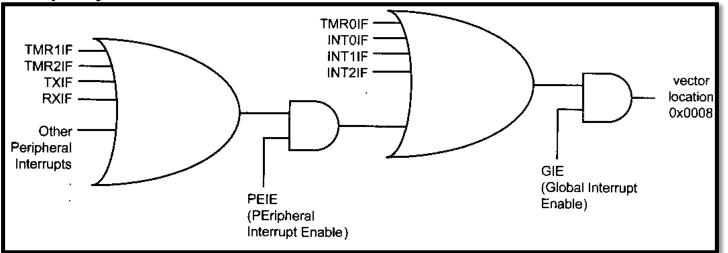

# **Simplified View of Interrupts**

- We can easily think of an interrupt as **two** digital signals:

- Enable bit can allow/disallow the actual interrupt from happening (Enabled = Unmasked, Disabled = Masked)

- 2. Flag bit is set if interrupt should be invoked (something happened)

- To make things confusing, some peripherals can be masked in a group by a PEIE mask

- By default, all interrupts are masked (disabled)

The PIC will not respond to any interrupts

- Up to the user to enable them if they are needed

- Enabling/disabling interrupts is done through designated registers in the SFR:

- INTCON, INTCON2, INTCON3

- RCON

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

- All interrupts can be masked by clearing the GIE

(Global Interrupt Enable) bit in INTCON (default) 17

- 1. Allow the specific interrupt to occur

- INTCONbits.TMR0IE = 1 (timer 0 can interrupt)

- INTCON3bits.INT1IE = 1 (INT 1 can interrupt)

- PIE1bits.ADIE = 1 (ADC can interrupt)

- 2. If specific interrupt falls into Peripheral category, must also enable another bit

INTCONbits.PEIE = 1

- 3. Allow any interrupt to occur

- INTCONbits.GIE = 1

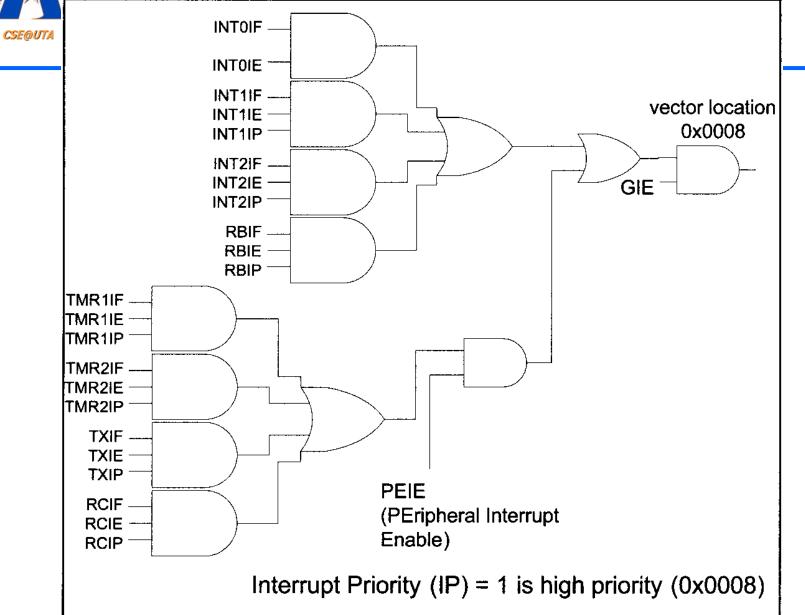

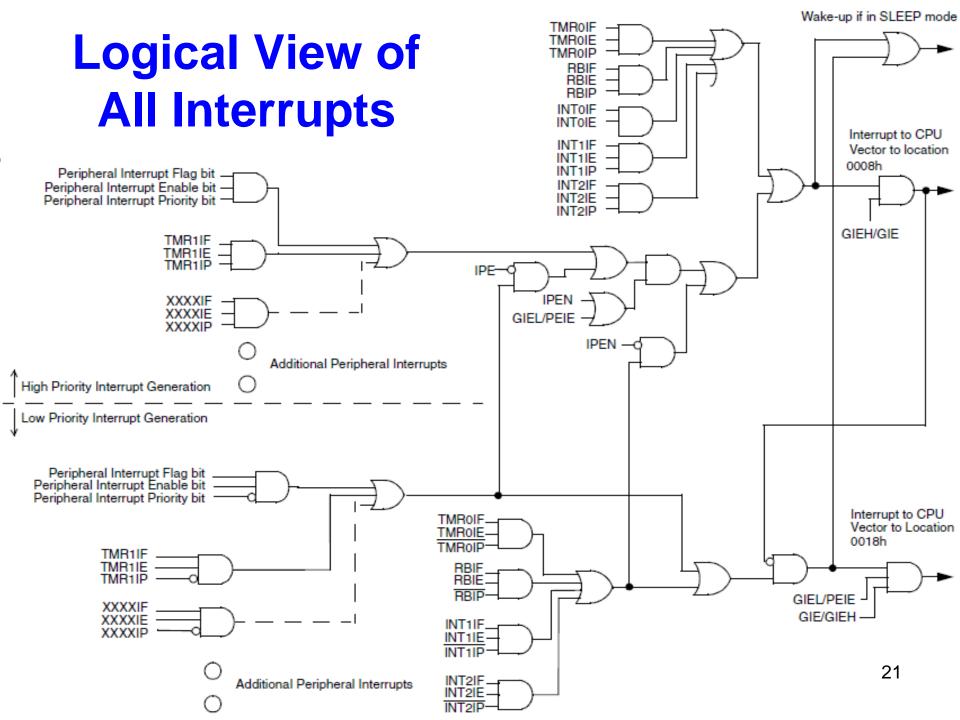

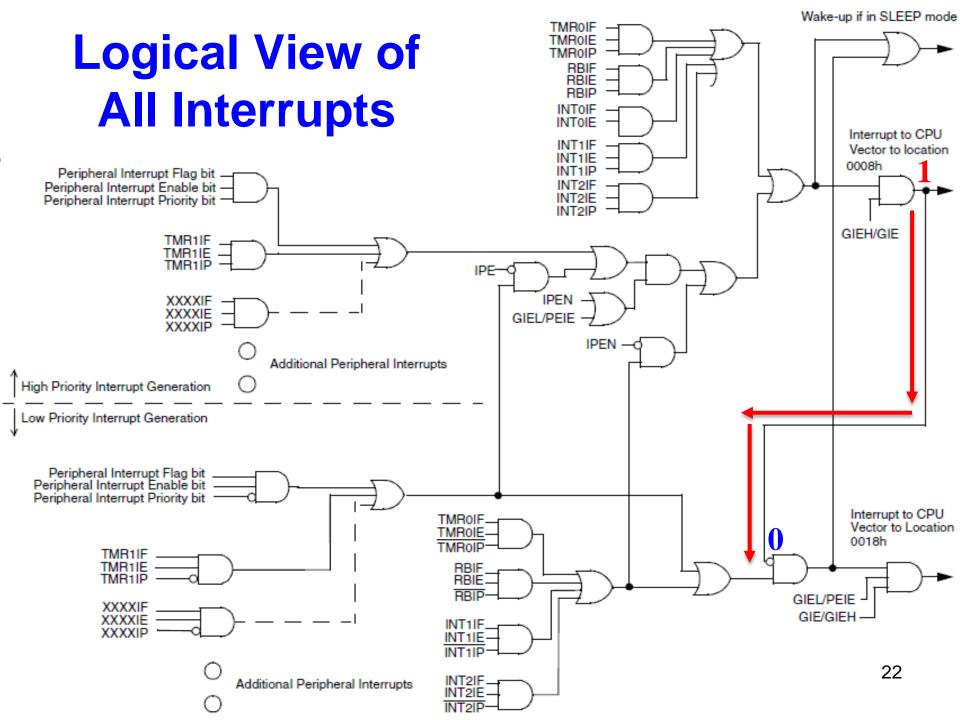

## Two Levels of Priorities RCONbits.IPEN

- The PIC18 has two levels of interrupts: HIGH and LOW

- By default (when reset) all interrupts are high priority (00008H)

- In RCON we can enable the two-level priority option

| 8-10: | RCON RE | RCON REGISTER |     |       |     |     |       |       |

|-------|---------|---------------|-----|-------|-----|-----|-------|-------|

|       | R/W-0   | U-0           | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|       | IPEN    |               | _   | RI    | TO  | PD  | POR   | BOR   |

|       | bit 7   |               |     |       | -   |     | ·     | bit 0 |

| bit 7 |         |               |     |       |     |     |       |       |

- Then we can assign low or high priority to interrupts by setting/clearing an interrupt priority bit in the IPRx SFRs

- This means there really are three bits controlling each interrupt

The INTO (RB0) hardware interrupt can only be of high priority

- Most importantly: When handling a low priority interrupt, high priority interrupts can steal the processor away 19

## **Logical View of High Priority Interrupts**

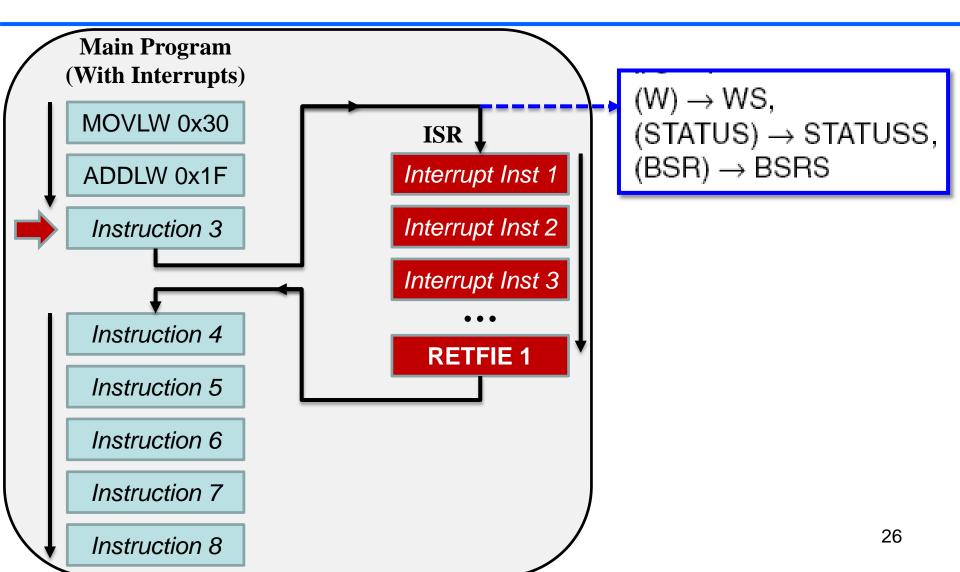

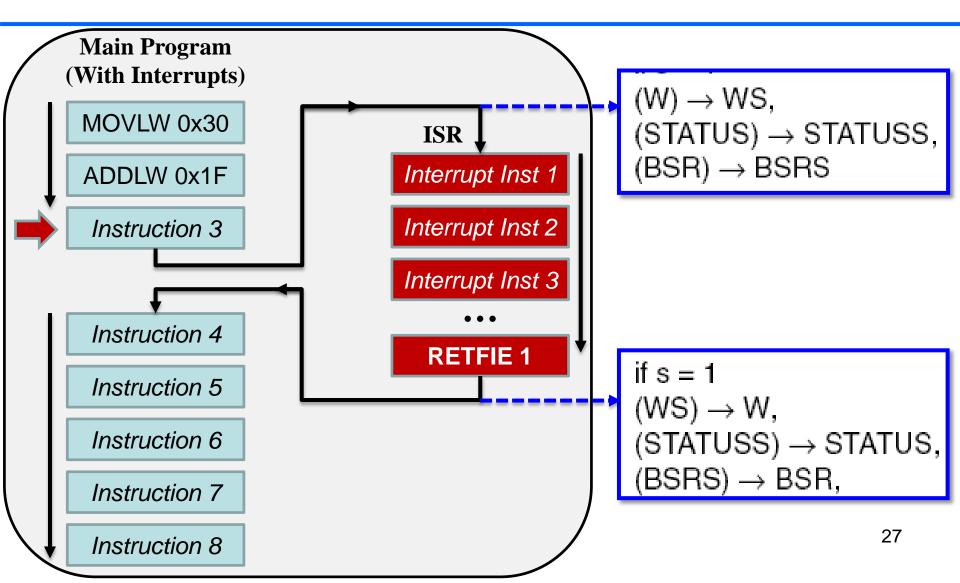

## What Happens to Other Important Registers?

- What happens to other important registers (**WREG**, **Status**, **BSR**) that may be impacted by an interrupt

- especially as they should be found the same way as they were left when returning

- The solution lies in the ISR having to save these registers at the beginning and restoring at the end

- High-Priority

- PIC18 automatically stores them in shadow registers

- To restore registers use RETFIE 1

- Low-Priority

- Programmer must store them manually

There is a one-deep shadow register set for WREG, Status, and BSR (similar to CALL and RETURN)

When jumping to High-Priority ISR

$\begin{array}{l} (\mathsf{W}) \rightarrow \mathsf{WS}, \\ (\mathsf{STATUS}) \rightarrow \mathsf{STATUSS}, \\ (\mathsf{BSR}) \rightarrow \mathsf{BSRS} \end{array}$

| RETFIE                                          | Return from Interrupt                                                                                                              |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                         | [ <i>label</i> ] RETFIE [s]                                                                                                        |

| Operands:                                       | s ∈ [0,1]                                                                                                                          |

| Operation:                                      | (TOS) $\rightarrow$ PC,<br>1 $\rightarrow$ GIE/GIEH or PEIE/GIEL,                                                                  |

| When<br>returning<br>from High-<br>Priority ISR | if s = 1<br>(WS) $\rightarrow$ W,<br>(STATUSS) $\rightarrow$ STATUS,<br>(BSRS) $\rightarrow$ BSR,<br>PCLATU, PCLATH are unchanged. |

| Status Affected:                                | GIE/GIEH, PEIE/GIEL.                                                                                                               |

# **Shadow Registers**

# **Shadow Registers**

# **Shadow Registers**

# **External INT Interrupts**

- INT0, INT1, and INT2 are all interrupts assigned to digital I/O pins

- To use them the corresponding TRISB bits have to be set

- INT interrupts are **edge triggered** (not level), thus a change must happen on the pins to trigger an interrupt

- Whether **rising** (default) or **falling edge** triggers the interrupt is software (INTCON2.INTEDGx bits) selectable

- When triggered (like many other flags) the ISR should explicitly clear the INTxIF flag

- INTO is always of high priority, the other two can be set

- Changes on RB4:RB7 can also cause interrupts but are on the group of the bits not individual

- Leaves B3 as the only PORTB pin without interrupt capability

- Interrupt priority can be set HIGH or LOW

- When handling interrupt, PORTB should be read and INTCON.RBIF should be cleared

- Great for...

- keyboard interfacing

- grouped input

- parallel input

#### **INTCON**

#### INTCON REGISTER

| R/W-  | -0                                                                | R/W-0                                           | R/W-0             | R/W-        | 0   | R/W-0                                    | R/W-0                                            | R/W-0                | R/W-x                |  |

|-------|-------------------------------------------------------------------|-------------------------------------------------|-------------------|-------------|-----|------------------------------------------|--------------------------------------------------|----------------------|----------------------|--|

| GIE/G | IEH                                                               | PEIE/GIEL                                       | TMROIE            | INTOI       | E   | RBIE                                     | TMR0IF                                           | INTOIF               | RBIF                 |  |

| bit 7 |                                                                   |                                                 |                   |             |     |                                          |                                                  |                      | bit 0                |  |

| bit 7 | GIE/0                                                             | GIEH: Global Interr                             | upt Enable bit    | bit         | t 3 | RBIE: RB Port Cha                        | ange Interrupt Enable                            | bit                  |                      |  |

|       | -                                                                 | <u>n IPEN = 0:</u><br>inables all unmask        | ed interrupts     |             |     |                                          | 3 port change interrup<br>B port change interrup |                      |                      |  |

|       | 0 = D                                                             | isables all interrup                            | ts                | bit         | t 2 | TMROIF: TMRO OV                          | verflow Interrupt Flag b                         | vit                  |                      |  |

|       | <u>When IPEN = 1:</u><br>1 = Enables all high priority interrupts |                                                 |                   |             |     | 1 = TMR0 register<br>0 = TMR0 register   | has overflowed (must<br>did not overflow         | be cleared in softwa | re)                  |  |

|       |                                                                   | isables all interrup                            |                   | bit         | t1  | INTOIF: INTO External Interrupt Flag bit |                                                  |                      |                      |  |

| bit 6 | PEIE                                                              | /GIEL: Peripheral I                             | nterrupt Enable b | pit         |     |                                          | nal interrupt occurred                           | ·                    | software)            |  |

|       | -                                                                 | <u>n IPEN = 0:</u>                              |                   |             |     |                                          | nal interrupt did not o                          | ccur                 |                      |  |

|       |                                                                   | nables all unmask<br>Disables all periphe       |                   | errupts bit | t 0 |                                          | ange Interrupt Flag bit<br>the RB7:RB4 pins cha  | inged state (must be | cleared in software) |  |

|       |                                                                   | 1  IPEN = 1:                                    | rai interrupts    |             |     |                                          | 37:RB4 pins have char                            | •                    | oleared in soltware) |  |

|       | 1 = E                                                             | inables all low prior<br>Disables all low prior |                   | •           |     |                                          |                                                  |                      |                      |  |

| bit 5 |                                                                   | 0IE: TMR0 Overflo                               | •                 |             |     |                                          |                                                  |                      |                      |  |

|       |                                                                   | nables the TMR0 o<br>Disables the TMR0          |                   |             |     |                                          |                                                  |                      |                      |  |

| bit 4 |                                                                   | IE: INTO External li                            |                   | it          |     |                                          |                                                  |                      | 20                   |  |

|       |                                                                   | nables the INT0 ex<br>bisables the INT0 e       |                   |             |     |                                          |                                                  |                      | 30                   |  |

## **INTCON2**

#### **18-2:** INTCON2 REGISTER

|       | R/W-1                                                                                   | R/W-1           | R/W-1         | R/W-1           | U-0           | R/W-1  | U-0 | R/W-1 |  |

|-------|-----------------------------------------------------------------------------------------|-----------------|---------------|-----------------|---------------|--------|-----|-------|--|

|       | RBPU                                                                                    | INTEDG0         | INTEDG1       | INTEDG2         | —             | TMR0IP | —   | RBIP  |  |

|       | bit 7                                                                                   |                 |               |                 |               |        |     | bit 0 |  |

|       |                                                                                         |                 |               |                 |               |        |     |       |  |

| bit 7 | RBPU: PC                                                                                | ORTB Pull-up    | Enable bit    |                 |               |        |     |       |  |

|       |                                                                                         | RTB pull-ups    |               |                 |               |        |     |       |  |

|       |                                                                                         |                 | -             | individual po   | rt latch valu | es     |     |       |  |

| bit 6 |                                                                                         | External Inte   |               | Select bit      |               |        |     |       |  |

|       |                                                                                         | ipt on rising e | -             |                 |               |        |     |       |  |

| 64 F  |                                                                                         | pt on falling   | •             | O a la at la it |               |        |     |       |  |

| bit 5 |                                                                                         | External Inte   |               | Select bit      |               |        |     |       |  |

|       | <ul> <li>1 = Interrupt on rising edge</li> <li>0 = Interrupt on falling edge</li> </ul> |                 |               |                 |               |        |     |       |  |

| bit 4 |                                                                                         | : External Inte | •             | Select bit      | -             | ┛┖     |     |       |  |

|       |                                                                                         | ipt on rising e |               |                 |               |        |     |       |  |

|       |                                                                                         | pt on falling   |               |                 |               |        |     |       |  |

| bit 3 | Unimplem                                                                                | nented: Read    | d as '0'      |                 |               |        |     |       |  |

| bit 2 | TMR0IP: 7                                                                               | TMR0 Overflo    | w Interrupt F | Priority bit    |               |        |     |       |  |

|       | 1 = High p                                                                              | oriority        |               |                 |               |        |     |       |  |

|       | 0 = Low p                                                                               | riority         |               |                 |               |        |     |       |  |

| bit 1 | Unimplem                                                                                | nented: Read    | d as '0'      |                 |               |        |     |       |  |

| bit 0 | RBIP: RB                                                                                | Port Change     | Interrupt Pri | ority bit       |               |        |     |       |  |

|       | 1 = High p                                                                              |                 |               |                 |               |        |     |       |  |

|       | 0 = Low pr                                                                              | riority         |               |                 |               |        |     |       |  |

## **INTCON3**

#### 18-3: INTCON3 REGISTER

|       | R/W-1                    | R/W-1          | U-0            | R/W-0     | R/W-0        | U-0       | R/W-0  | R/W-0  |

|-------|--------------------------|----------------|----------------|-----------|--------------|-----------|--------|--------|

|       | INT2IP                   | INT1IP         | —              | INT2IE    | INT1IE       | —         | INT2IF | INT1IF |

|       | bit 7                    |                |                |           |              |           |        | bit 0  |

|       |                          |                |                |           |              |           |        |        |

| bit 7 | INT2IP: IN               | IT2 External I | nterrupt Prio  | rity bit  |              |           |        |        |

|       | 1 = High p<br>0 = Low pr |                |                |           |              |           |        |        |

| bit 6 | INT1IP: IN               | IT1 External I | nterrupt Prio  | rity bit  |              |           |        |        |

|       | 1 = High p               |                |                |           |              |           |        |        |

|       | 0 = Low pr               |                |                |           |              |           |        |        |

| bit 5 | Unimplem                 | nented: Read   | l as '0'       |           |              |           |        |        |

| bit 4 | INT2IE: IN               | IT2 External I | nterrupt Ena   | ble bit   |              |           |        |        |

|       |                          | es the INT2 e  |                |           |              |           |        |        |

|       |                          | es the INT2 e  |                |           |              |           |        |        |

| bit 3 |                          | IT1 External I |                |           |              |           |        |        |

|       |                          | es the INT1 e  |                |           |              |           |        |        |

|       |                          | es the INT1 e  |                | rupt      |              |           |        |        |

| bit 2 | Unimplem                 | nented: Read   | l as '0'       |           |              |           |        |        |

| bit 1 | INT2IF: IN               | T2 External I  | nterrupt Flag  | bit       |              |           |        |        |

|       |                          | T2 external i  | •              |           | e cleared in | software) |        |        |

|       | 0 = The IN               | T2 external i  | nterrupt did n | not occur |              |           |        |        |

| bit 0 | INT1IF: IN               | T1 External I  | nterrupt Flag  | bit       |              |           |        |        |

|       |                          | T1 external i  |                |           | e cleared in | software) |        |        |

0 = The INT1 external interrupt did not occur

REGISTER 8-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

|       | R/W-0                                                                                                                                 | R/W-0                           | <b>R</b> -0  | R-0          | R/W-0         | R/W-0        | R/W-0       | R/W-0      |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------|--------------|---------------|--------------|-------------|------------|--|--|--|

|       | PSPIF <sup>(1)</sup>                                                                                                                  | ADIF                            | RCIF         | TXIF         | SSPIF         | CCP1IF       | TMR2IF      | TMR1IF     |  |  |  |

|       | bit 7                                                                                                                                 |                                 |              |              |               |              |             | bit 0      |  |  |  |

|       |                                                                                                                                       |                                 |              |              |               |              |             |            |  |  |  |

| bit 7 |                                                                                                                                       | Parallel Slave                  |              |              |               |              |             |            |  |  |  |

|       |                                                                                                                                       | or a write op<br>d or write has |              | aken place ( | must be cle   | ared in soft | ware)       |            |  |  |  |

| bit 6 |                                                                                                                                       | Converter Int                   |              | oit          |               |              |             |            |  |  |  |

| bito  |                                                                                                                                       | conversion                      | 1 0          |              | ed in softwa  | are)         |             |            |  |  |  |

|       |                                                                                                                                       | D conversion                    |              |              |               | ,            |             |            |  |  |  |

| bit 5 |                                                                                                                                       | RT Receive                      |              |              |               |              |             |            |  |  |  |

|       |                                                                                                                                       | SART receive                    |              |              | eared wher    | n RCREG is   | s read)     |            |  |  |  |

| bit 4 |                                                                                                                                       | RT Transmit                     |              |              | ction 16.0 f  | or dotaile o | n TXIE fund | tionality) |  |  |  |

| 511 4 |                                                                                                                                       | SART transmit                   |              |              |               |              |             |            |  |  |  |

|       |                                                                                                                                       | SART transm                     |              |              | (             |              |             | /          |  |  |  |

| bit 3 |                                                                                                                                       | ster Synchro                    |              |              | -             |              |             |            |  |  |  |

|       | <ul> <li>1 = The transmission/reception is complete (must be cleared in software)</li> <li>0 = Waiting to transmit/receive</li> </ul> |                                 |              |              |               |              |             |            |  |  |  |

| bit 2 | -                                                                                                                                     | CP1 Interrup                    |              |              |               |              |             |            |  |  |  |

| DIL Z | Capture mo                                                                                                                            |                                 | t Flag bit   |              |               |              |             |            |  |  |  |

|       | 1 = A TMR                                                                                                                             | 1 register ca                   |              |              | cleared in se | oftware)     |             |            |  |  |  |

|       |                                                                                                                                       | R1 register c                   | apture occur | red          |               |              |             |            |  |  |  |

|       | $\frac{\text{Compare n}}{1 - \Lambda \text{TMP}}$                                                                                     | <u>node:</u><br>1 register co   | mnara matak  | occurred (n  | ust he clea   | rad in coffu |             |            |  |  |  |

|       |                                                                                                                                       | R1 register co                  |              |              | lust be clea  |              | vale)       |            |  |  |  |

|       | PWM mode                                                                                                                              | •                               |              |              |               |              |             |            |  |  |  |

|       | Unused in                                                                                                                             | this mode                       |              |              |               |              |             |            |  |  |  |

| bit 1 |                                                                                                                                       | MR2 to PR2                      |              |              |               | ,            |             |            |  |  |  |

|       |                                                                                                                                       | to PR2 matcl<br>R2 to PR2 m     | •            |              | red in softwa | are)         |             |            |  |  |  |

| bit 0 |                                                                                                                                       | MR1 Overflo                     |              | -            |               |              |             |            |  |  |  |

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = MR1 register did not overflow

#### REGISTER 8-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0         | R/W-0  |

|-------|-----|-----|-------|-------|-------|---------------|--------|

| _     | —   | _   | EEIF  | BCLIF | LVDIF | <b>TMR3IF</b> | CCP2IF |

| bit 7 | •   |     |       | •     | •     |               | bit 0  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | EEIF: Data EEPROM/FLASH Write Operation Interrupt Flag bit<br>1 = The Write operation is complete (must be cleared in software)<br>0 = The Write operation is not complete, or has not been started                                                                                                                                           |

| bit 3   | BCLIF: Bus Collision Interrupt Flag bit<br>1 = A bus collision occurred (must be cleared in software)<br>0 = No bus collision occurred                                                                                                                                                                                                        |

| bit 2   | LVDIF: Low Voltage Detect Interrupt Flag bit<br>1 = A low voltage condition occurred (must be cleared in software)<br>0 = The device voltage is above the Low Voltage Detect trip point                                                                                                                                                       |

| bit 1   | TMR3IF: TMR3 Overflow Interrupt Flag bit<br>1 = TMR3 register overflowed (must be cleared in software)<br>0 = TMR3 register did not overflow                                                                                                                                                                                                  |

| bit 0   | CCP2IF: CCPx Interrupt Flag bit<br><u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM mode:</u> |

|         | Unused in this mode                                                                                                                                                                                                                                                                                                                           |

#### PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |   |

|----------------------|-------|-------|-------|-------|--------|--------|--------|---|

| PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | Ι |

| bit 7                |       | •     | •     |       |        |        | bit 0  | - |

| bit 7 | <b>PSPIE:</b> Parallel Slave Port Read/Write Interrupt Enable bit<br>1 = Enables the PSP read/write interrupt<br>0 = Disables the PSP read/write interrupt | bit 3 | SSPIE: Master Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the MSSP interrupt<br>0 = Disables the MSSP interrupt               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                                                                                                                   | bit 2 | CCP1IE: CCP1 Interrupt Enable bit                                                                                                             |

|       | <ul> <li>1 = Enables the A/D interrupt</li> <li>0 = Disables the A/D interrupt</li> </ul>                                                                  |       | <ul> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> </ul>                                                   |

| bit 5 | <b>RCIE:</b> USART Receive Interrupt Enable bit<br>1 = Enables the USART receive interrupt<br>0 = Disables the USART receive interrupt                     | bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |

| bit 4 | <b>TXIE:</b> USART Transmit Interrupt Enable bit<br>1 = Enables the USART transmit interrupt<br>0 = Disables the USART transmit interrupt                  | bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit<br>1 = Enables the TMR1 overflow interrupt<br>0 = Disables the TMR1 overflow interrupt             |

#### REGISTER 8-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

|                                                                                                               | U-0                                            | U-0         | U-0        | R/W-0       | R/W-0        | R/W-0    | R/W-0         | R/W-0  |  |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------|------------|-------------|--------------|----------|---------------|--------|--|

|                                                                                                               | —                                              | —           | _          | EEIE        | BCLIE        | LVDIE    | <b>TMR3IE</b> | CCP2IE |  |

|                                                                                                               | bit 7                                          |             |            |             |              |          |               | bit 0  |  |

|                                                                                                               |                                                |             |            |             |              |          |               |        |  |

| bit 7-5                                                                                                       | Unimplemented: Read as '0'                     |             |            |             |              |          |               |        |  |

| bit 4                                                                                                         | EEIE: Data                                     | EEPROM/F    | LASH Write | e Operation | Interrupt En | able bit |               |        |  |

|                                                                                                               |                                                |             |            |             |              |          |               |        |  |

|                                                                                                               | 0 = Disabled                                   |             |            |             |              |          |               |        |  |

| bit 3 BCLIE: Bus Collision Interrupt Enable bit                                                               |                                                |             |            |             |              |          |               |        |  |

|                                                                                                               |                                                | 1 = Enabled |            |             |              |          |               |        |  |

| 0 = Disabled                                                                                                  |                                                |             |            |             |              |          |               |        |  |

| bit 2                                                                                                         | LVDIE: Low Voltage Detect Interrupt Enable bit |             |            |             |              |          |               |        |  |

|                                                                                                               | 1 = Enabled<br>0 = Disabled                    |             |            |             |              |          |               |        |  |

| bit 1                                                                                                         |                                                |             |            |             |              |          |               |        |  |

| DILI                                                                                                          | TMR3IE: TMR3 Overflow Interrupt Enable bit     |             |            |             |              |          |               |        |  |

| <ul> <li>1 = Enables the TMR3 overflow interrupt</li> <li>0 = Disables the TMR3 overflow interrupt</li> </ul> |                                                |             |            |             |              |          |               |        |  |

| bit 0                                                                                                         |                                                | CP2 Interru |            |             |              |          |               |        |  |

| DIEU                                                                                                          |                                                | s the CCP2  |            |             |              |          |               | 36     |  |

|                                                                                                               |                                                | s the CCP2  |            |             |              |          |               |        |  |

|                                                                                                               |                                                |             | -          |             |              |          |               |        |  |

#### REGISTER 8-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

|       | <b>R/W-1</b>                                                 | R/W-1 | R/W-1          | R/W-1                                   | R/W-1        | R/W-1  | R/W-1  | R/W-1  |  |

|-------|--------------------------------------------------------------|-------|----------------|-----------------------------------------|--------------|--------|--------|--------|--|

|       | PSPIP <sup>(1)</sup>                                         | ADIP  | RCIP           | TXIP                                    | SSPIP        | CCP1IP | TMR2IP | TMR1IP |  |

|       | bit 7                                                        |       |                |                                         |              |        |        | bit 0  |  |

|       |                                                              |       |                |                                         |              |        |        |        |  |

| bit 7 | PSPIP <sup>(1)</sup> : P                                     |       | e Port Read    | /Write Interr                           | upt Priority | bit    |        |        |  |

|       | 1 = High pri<br>0 = Low pri                                  |       |                |                                         |              |        |        |        |  |

| bit 6 | ADIP: A/D Converter Interrupt Priority bit                   |       |                |                                         |              |        |        |        |  |

| Dit 0 | 1 = High priority                                            |       |                |                                         |              |        |        |        |  |

|       | 0 = Low priority                                             |       |                |                                         |              |        |        |        |  |

| bit 5 | RCIP: USART Receive Interrupt Priority bit                   |       |                |                                         |              |        |        |        |  |

|       | 1 = High priority<br>0 = Low priority                        |       |                |                                         |              |        |        |        |  |

| bit 4 |                                                              |       | Interrupt P    | riority bit                             |              |        |        |        |  |

| DIL 4 | 1 = High pri                                                 |       | menupin        | nonty bit                               |              |        |        |        |  |

|       | 0 = Low pri                                                  |       |                |                                         |              |        |        |        |  |

| bit 3 | SSPIP: Master Synchronous Serial Port Interrupt Priority bit |       |                |                                         |              |        |        |        |  |

|       | 1 = High priority<br>0 = Low priority                        |       |                |                                         |              |        |        |        |  |

| bit 2 | CCP1IP: C                                                    |       | ot Priority bi |                                         |              |        |        |        |  |

| DIT Z | 1 = High pri                                                 |       | or i nonty bi  | L C C C C C C C C C C C C C C C C C C C |              |        |        |        |  |

|       | 0 = Low pri                                                  |       |                |                                         |              |        |        |        |  |

| bit 1 |                                                              |       | Match Inter    | rrupt Priority                          | bit          |        |        |        |  |

|       | 1 = High pri<br>0 = Low pri                                  |       |                |                                         |              |        |        |        |  |

| bit 0 |                                                              |       | w Interrupt    | Driority bit                            |              |        |        |        |  |

| DILU  | 1 = High pri                                                 |       | w interrupt    |                                         |              |        |        |        |  |

|       | 0 = Low pri                                                  |       |                |                                         |              |        |        |        |  |

37

#### REGISTER 8-9: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1  |

|-------|-----|-----|-------|-------|-------|--------|--------|

| —     | —   | —   | EEIP  | BCLIP | LVDIP | TMR3IP | CCP2IP |

| bit 7 | •   | •   |       |       |       | •      | bit 0  |

| bit 7-5 | Unimplemented: Read as '0'                                                                              |

|---------|---------------------------------------------------------------------------------------------------------|

| bit 4   | EEIP: Data EEPROM/FLASH Write Operation Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |

| bit 3   | BCLIP: Bus Collision Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                    |

| bit 2   | LVDIP: Low Voltage Detect Interrupt Priority bit<br>1 = High priority<br>0 = Low priority               |

| bit 1   | TMR3IP: TMR3 Overflow Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                   |

| bit 0   | CCP2IP: CCP2 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                            |

REGISTER 8-10: RCON REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | —   | —   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 | •   |     |       | •   |     |       | bit 0 |

| bit 7   | IPEN: Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (16CXXX Compatibility mode) |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                               |

| bit 4   | RI: RESET Instruction Flag bit                                                                                                                           |

|         | For details of bit operation, see Register 4-3                                                                                                           |

| bit 3   | TO: Watchdog Time-out Flag bit                                                                                                                           |

|         | For details of bit operation, see Register 4-3                                                                                                           |

| bit 2   | PD: Power-down Detection Flag bit                                                                                                                        |

|         | For details of bit operation, see Register 4-3                                                                                                           |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                           |

|         | For details of bit operation, see Register 4-3                                                                                                           |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                          |

|         | For details of bit operation, see Register 4-3                                                                                                           |

|         |                                                                                                                                                          |

• Really just a quasi-tedious job of setting the right bits in the right registers and "org"-ing the code at the right place

ORG 0000H GOTO MAIN

ORG 0008H GOTO HP\_ISR

ORG 00018H GOTO LP\_ISR

. . .

HP\_ISR

ORG 200H BTFSS INTCON, INTOIF RETFIE 1 BTG PORTB, 7 BCF INTCON, INTOIF RETFIE 1

... BSF INTCON, INTOIE BCF INTCON2, INTEDG0 BSF INTCON, GIE

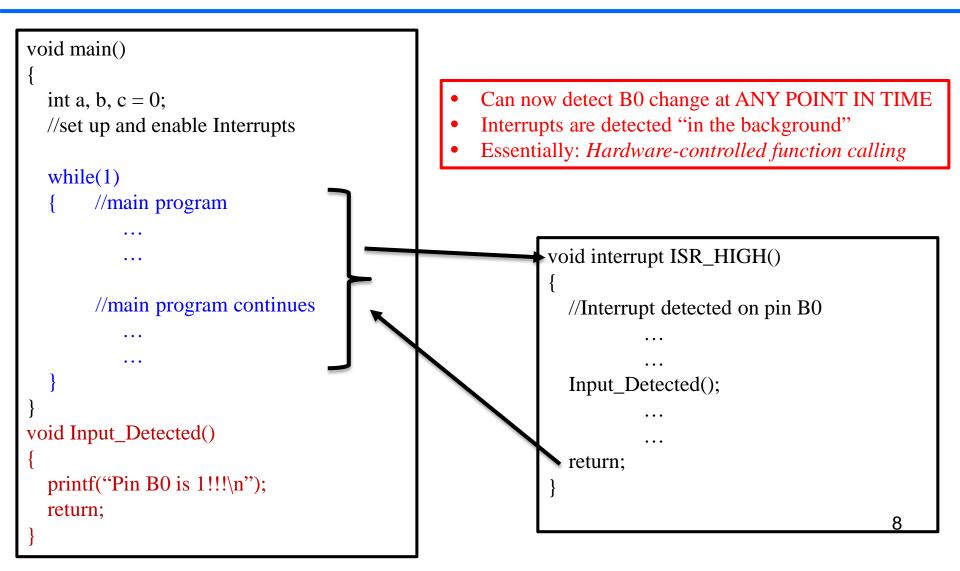

# Interrupt Programming from C

- We need to define functions that are for high priority and low priority ISRs

- We need to make sure that our ISRs are in the right place

- We do not need to worry about context-switching, the C compiler is going to make sure our registers are properly handled and variables that need saving are saved

- Interrupt handlers should start off with an "if" or a "switch-case" complex to identify the source of the interrupt

## **Defining ISRs in C18**

- Defining functions that are for high priority and low priority ISRs:

- At the beginning of the program, have a prototype of all functions (including ISRs)

- Use #pragma interrupt function\_name and #pragma interruptlow function\_name to tell C18 compiler that a function is an interrupt function (so it can use proper RETFIE returns and fast context switching)

## Placing ISRs in C18

- Make sure that our ISRs are in the right place

- At the beginning of the code insert goto instructions to the interrupt vectors

- Use ASM to limit size and ensure it fits in ROM

```

#pragma code My_Hi_Priority_Int = 0x0008

void My_Hi_Priority_Int(void)

{

_asm

GOTO chk_isr

_endasm

}

```

# **Interrupt Handling in C18**

```

#include <P18F452.h>

void main()

ł

void My ISR High(void);

//main control code

//and Interrupt Settings

void My ISR Low(void);

. . .

#pragma code My Hi Priority Int = 0x0008

}

void My Hi Priority Int(void)

//other functions

{

asm

. . .

GOTO My ISR High

endasm

}

#pragma interrupt My ISR High

void My ISR High(void)

#pragma code My_Lo_Priority_Int = 0x00018

{

void My Lo Priority Int(void)

//interrupt handling for HIGH

{

. . .

_asm

}

GOTO My ISR Low

endasm

#pragma interruptlow My ISR Low

}

void My ISR Low(void)

{

//interrupt handling for LOW

44

. . .

```

}

### Placing ISRs in XC8

- Much simpler in XC8 compiler

- Only need to know two keywords

- "interrupt" and "low\_priority"

#### High-Priority

#### Low-Priority

```

void interrupt low_priority My_ISR_Low(void)

{

//interrupt handling for LP

}

```

# **Interrupt Handling in XC8**

```

#include <P18F452.h>

void interrupt My ISR High(void)

{

void My ISR High(void);

//interrupt handling for HIGH

if(INT0IF == 1 && INT0IE == 1)

void My ISR Low(void);

//INT0 interrupt tripped

if(TMR0IF == 1 && TMR0IE == 1)

void main()

//Timer 0 interrupt tripped

{

//main control code

. . .

//and Interrupt Settings

}

. . .

}

void interrupt low priority My ISR Low(void)

//other functions

{

//interrupt handling for LOW

. . .

if(ADIF == 1 && ADIE == 1)

//ADC conversion done

if(INT1IF == 1 && INT1IE == 1)

//placing of interrupt code at the

//INT1 interrupt tripped

correct locations is automatically

if(RCIF == 1 && RCIE == 1)

handled by the XC8 compiler

//Serial reception occurred

. . .

```

}

#### **ADC Interrupt Example**

}

```

#include <P18F452.h>

void My ISR High(void);

void main()

{

ADCON1 = 0b11001110; //ADC settings

ADCON0 = 0b1000001;

PIR1bits.ADIF = 0; //Clear ADIF flag bit

IPR1bits.ADIP = 1; //ADC is HIGH Priority

PIE1bits.ADIE = 1; //Set ADIE enable bit

INTCONbits.PEIE = 1; //Set PEIE enable bit

INTCONbits.GIE = 1; //Set GIE enable bit

while(1)

{

ADCONØbits.GO = 1; //Start ADC

...// go on with other code

. . .

}

```

```

void interrupt My ISR High(void)

//interrupt handling for HIGH

if(INT0IF == 1 && INT0IE == 1)

//INT0 interrupt tripped

if(ADIF == 1 && ADIE == 1)

{

//ADC conversion done

//Get result from ADRESH/L

PIR1bits.ADIF = 0; //clear flag

}

```

#### **Summary**

- Interrupts are a great way to handle peripheral attention or external happenings

- Some of the most used interrupts are timers (later), external hardware, serial communications, and ADC ready

- All interrupts in the PIC18 can be masked in a group or individually

- We can have two levels of priorities, with an almost fully configurable what interrupt belong to what level relationship

- Programming ISRs from C requires knowledge of how the compiler is told about ISRs

- Consult the compiler's user guide for specifics